12月11日~12日,奇捷科技(Easy-Logic Technology)受邀参加集成电路设计业年度盛会——上海集成电路2024年度产业发展论坛暨第三十届集成电路设计业展览会”(ICCAD-Expo 2024),与来自各地的行业同仁齐聚上海,共同探讨集成电路产业特别是IC设计业未来发展机遇和挑战,分享实战经验与创新成果。

在国际竞争加剧和全球芯片产业格局重塑的当下,如何在成本压力和市场快速变化中保持竞争力,成为了企业亟需解决的难题。在此背景下,ECO设计方法显得尤为重要,为芯片设计领域提供了节省时间和成本的有效解决方案。12月12日,在“EDA与IC设计”专题论坛中,奇捷科技CEO魏星博士也针对这一需求发表了《深耕增量式设计流程应用,赋能EDA创芯发展》的专题演讲。

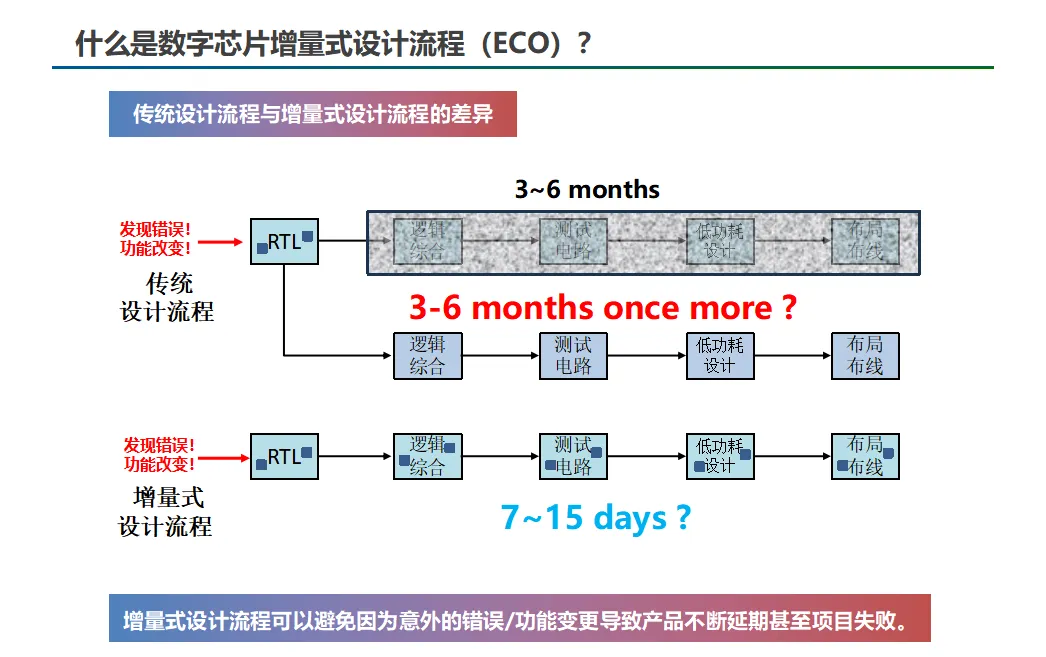

什么是增量式设计呢,魏星博士介绍,芯片设计项目完成布局、布线等物理操作,甚至已经流片了,发现需要修改设计规格(RTL代码)。传统做法是重走一遍设计流程,然而现代数字芯片设计规格非常复杂,这种方式会耗费大量时间,造成项目延迟。

所以更加经济有效的做法是,通过增量式设计方法,以嵌入局部逻辑补丁的方式,直接对门级网表的逻辑功能进行必要的变更,从而控制项目周期,这就是我们所说的ECO。

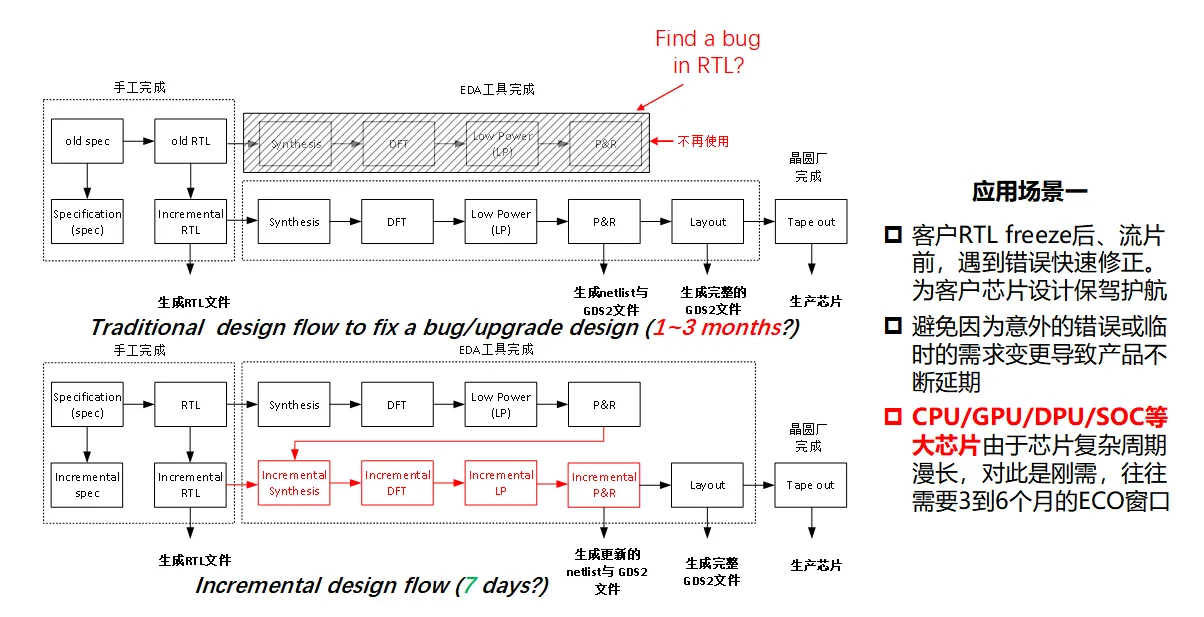

魏星博士提到,增量式设计流程主要三种应用场景,一种是当项目进入到中后期,当出现意外的RTL错误或者设计规格变更时,帮助产品在计划时间内完成。

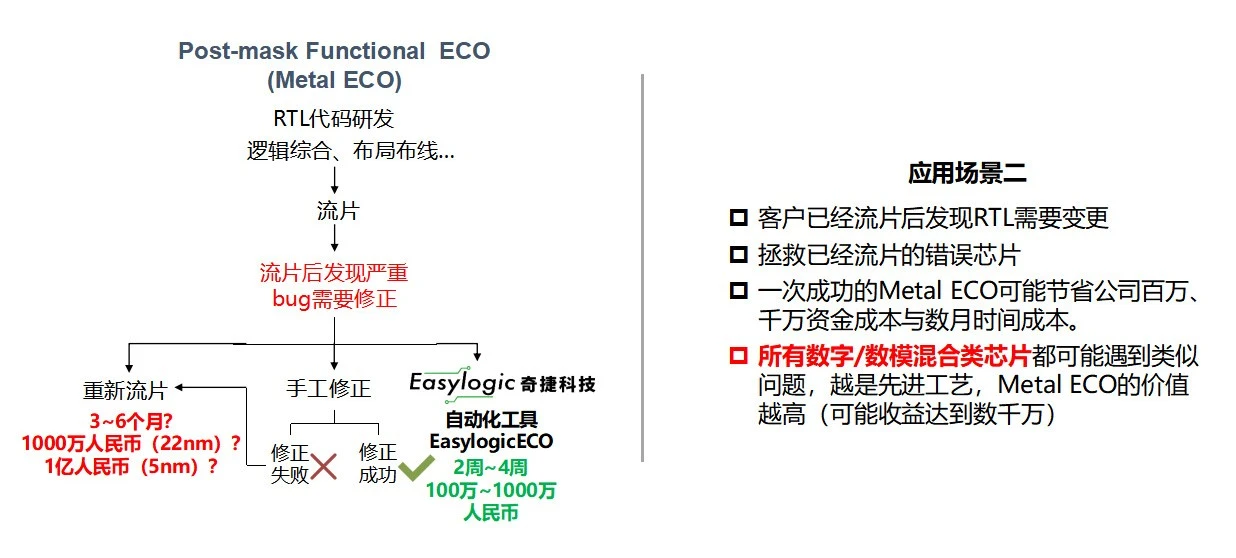

另一种场景是拯救已经流片的错误芯片(这种场景一般称为Metal ECO),利用预先留好的备用单元搭配金属层连线来修改电路结构,从而帮助客户解决错误芯片难题。

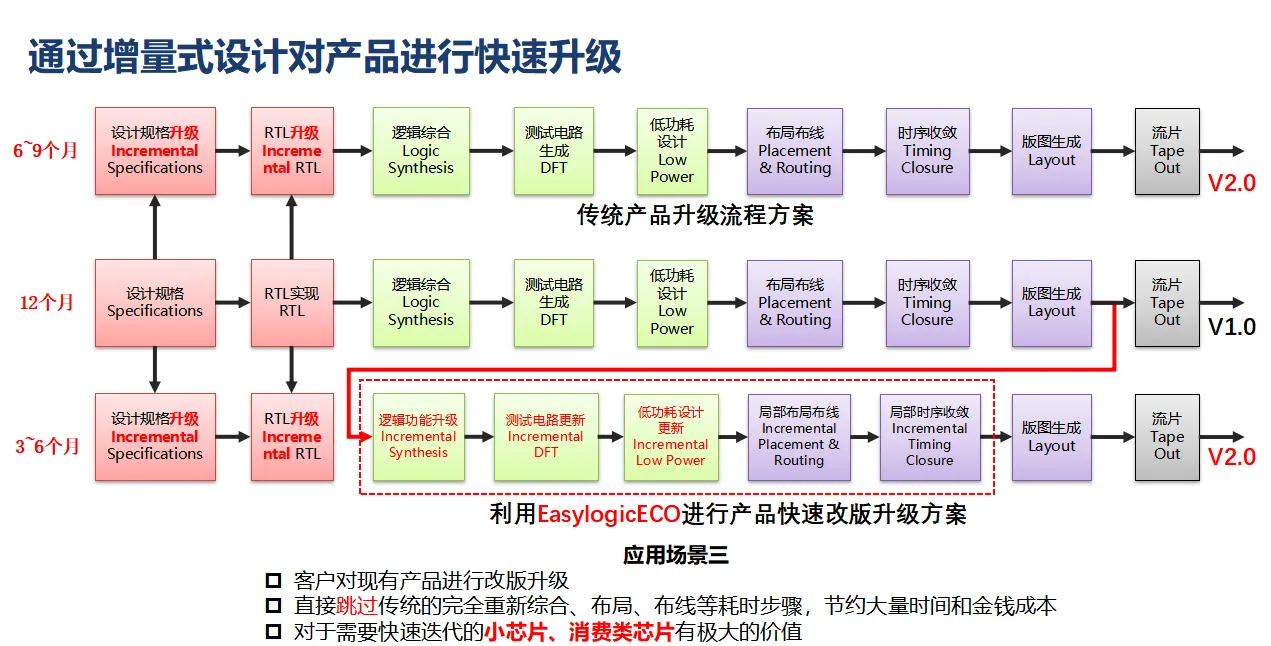

第三种是改版升级场景,在芯片需要进行升级迭代时,跳过传统的完全重新综合、布局布线等耗时操作,在前置工作准备充分的条件下,直接在上一版本的最终结果网表上进行局部修改,以满足升级后的功能需求,从而节省大量时间和金钱成本。

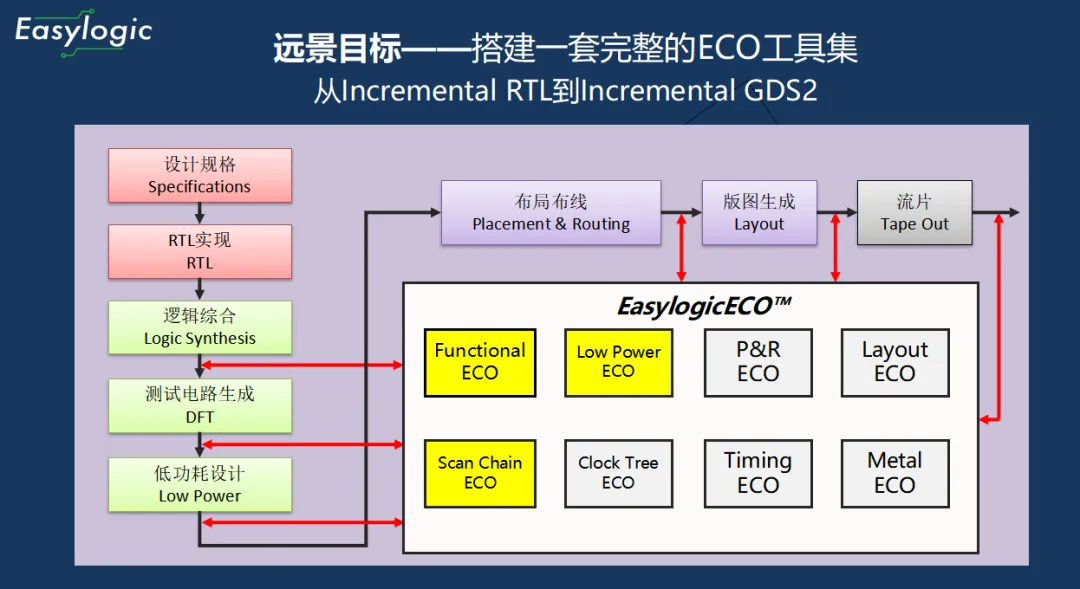

随着其重要性越发凸显,如何搭建一个行之有效的ECO流程也受到越来越多企业的重视。魏星博士针对ECO也提出几点建议,比如避免积累多个ECO任务合并解决,防止不同的ECO问题互相影响、由专人负责并建立系统化ECO流程、编写自动化脚本运行ECO工具等等。奇捷科技也将继续身体力行,利用其行业积累及技术优势,搭建一整套完整的ECO工具集,为行业带来相关规范,助力企业降本增效。

展会现场,奇捷科技工作人员与参展嘉宾详细介绍了EasylogicECO产品功能,针对不同的业务场景及解决方案进行了深入的探讨,吸引了众多行业内专业人士驻足参观交流及互动抽奖。

此次展会的成功举办,奇捷科技向更多客户展示了其可靠且高效的ECO解决方案,也期待未来能与各产业同仁有更多的合作与交流。